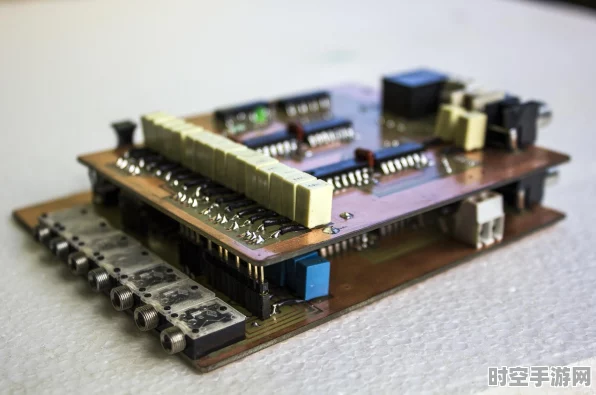

FPGA 复位在电子设计中至关重要,掌握有效的复位技巧能让您的设计更加稳定可靠,我们将深入探讨这 8 种实用的 FPGA 复位技巧。

中心句:FPGA 复位对于电子设计的重要性不言而喻。

复位信号的同步处理是关键技巧之一,在 FPGA 设计中,异步复位信号可能引入亚稳态问题,因此将复位信号进行同步处理能够有效避免这些潜在风险,通过使用同步器,将异步复位信号转换为同步复位信号,确保系统在复位时的稳定性。

中心句:复位信号的同步处理能避免亚稳态问题,保证系统稳定。

另一种有效的技巧是复位释放的控制,合理地控制复位释放的时间和条件,能防止在系统不稳定时过早释放复位,从而避免出现错误的操作或不稳定的状态,可以根据时钟计数或者特定的状态标志来决定复位的释放时机。

中心句:合理控制复位释放可防止系统不稳定时的错误操作。

多时钟域中的复位处理也是需要特别关注的,不同时钟域之间的复位信号传递需要特殊的处理方式,以确保复位的准确性和有效性,可以采用跨时钟域的同步技术或者专门的复位管理模块来解决这个问题。

中心句:多时钟域中的复位处理需特殊方式确保准确性和有效性。

复位的优先级设置也不能忽视,在复杂的系统中,可能存在多个复位源,合理设置它们的优先级,能够保证在不同情况下系统都能按照预期进行复位操作。

中心句:复位的优先级设置影响复杂系统的复位操作预期。

监控和诊断复位状态也是重要的一环,通过添加相应的监控电路和诊断模块,可以实时了解复位的状态和是否出现异常,以便及时采取措施进行修复和调整。

中心句:监控和诊断复位状态有助于及时发现和解决异常。

还有,复位的可靠性设计也必不可少,采用冗余的复位机制或者容错设计,能够在出现故障时仍然保证复位功能的正常运行,提高系统的整体可靠性。

中心句:复位的可靠性设计增强系统应对故障的能力。

考虑功耗优化在复位设计中也有其价值,通过合理的控制复位电路的功耗,可以降低整个系统的能耗,特别是在对功耗要求严格的应用场景中。

中心句:功耗优化在复位设计中能降低系统能耗。

掌握这 8 种 FPGA 复位技巧,并在实际设计中灵活运用,将为您打造出更加稳定、高效的 FPGA 系统提供有力的支持。

文章参考来源:相关电子设计技术书籍及专业论坛交流。