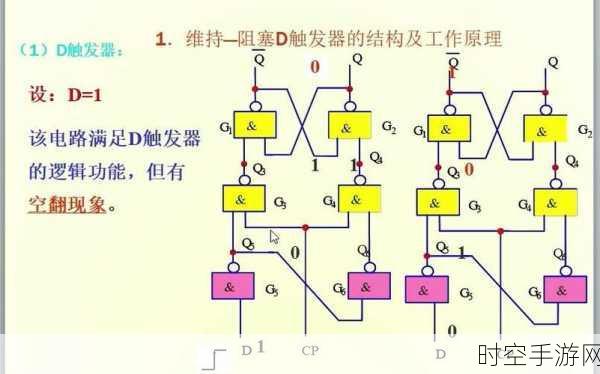

在数字电路的世界里,触发器是一个至关重要的组成部分,其中的空翻现象却常常给电路设计带来困扰,究竟是什么导致了这一现象的出现呢?

空翻现象指的是在一个时钟脉冲周期内,触发器发生多次翻转的情况,这一现象会严重影响数字电路的稳定性和可靠性。

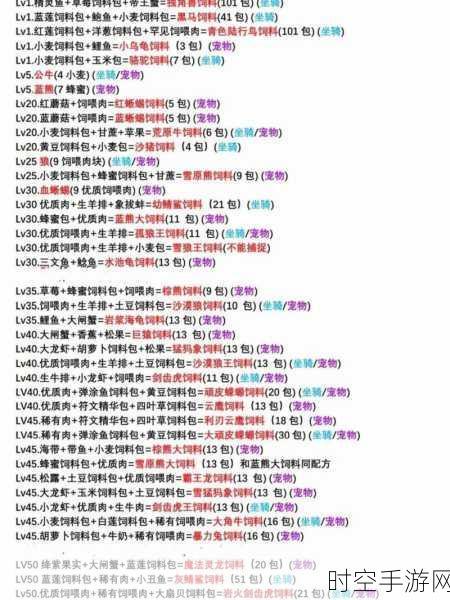

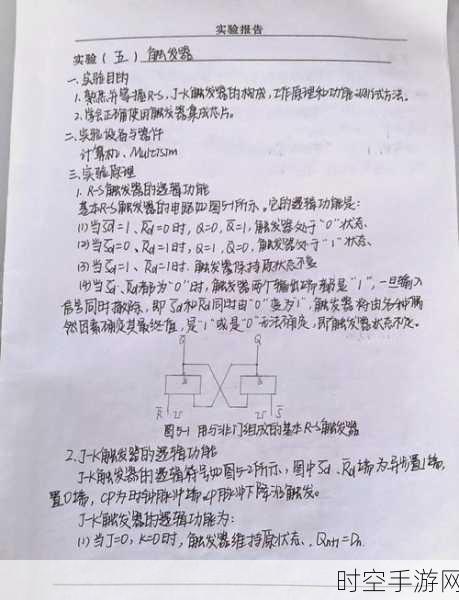

造成数字电路触发器空翻现象的原因主要有以下几个方面,其一,触发器的电路结构设计不合理,在某些结构中,输入信号的变化可能会直接导致触发器状态的多次改变,其二,时钟信号的不稳定也是一个重要因素,若时钟脉冲的宽度过宽或者频率过高,都有可能引发空翻,其三,外部干扰的存在同样不容忽视,外界的电磁干扰等可能影响触发器的正常工作,从而导致空翻现象。

为了避免数字电路触发器的空翻现象,我们可以采取一些有效的措施,在电路设计阶段,要精心规划触发器的结构,确保其合理性和稳定性,要对时钟信号进行严格的控制和优化,保证其宽度和频率符合设计要求,还应当加强电路的抗干扰能力,通过屏蔽、滤波等手段减少外部干扰的影响。

深入了解数字电路触发器的空翻现象及原因,对于提高数字电路的性能和可靠性具有重要意义,我们只有掌握了这些知识,才能在电路设计中更好地避免空翻问题,实现电路的稳定运行。

文章参考来源:数字电路相关教材及专业论文。